- 您现在的位置:买卖IC网 > Sheet目录1991 > CS5342-CZZ (Cirrus Logic Inc)IC ADC AUD 105DB 200KHZ 16-TSSOP

10

DS608F1

CS5342

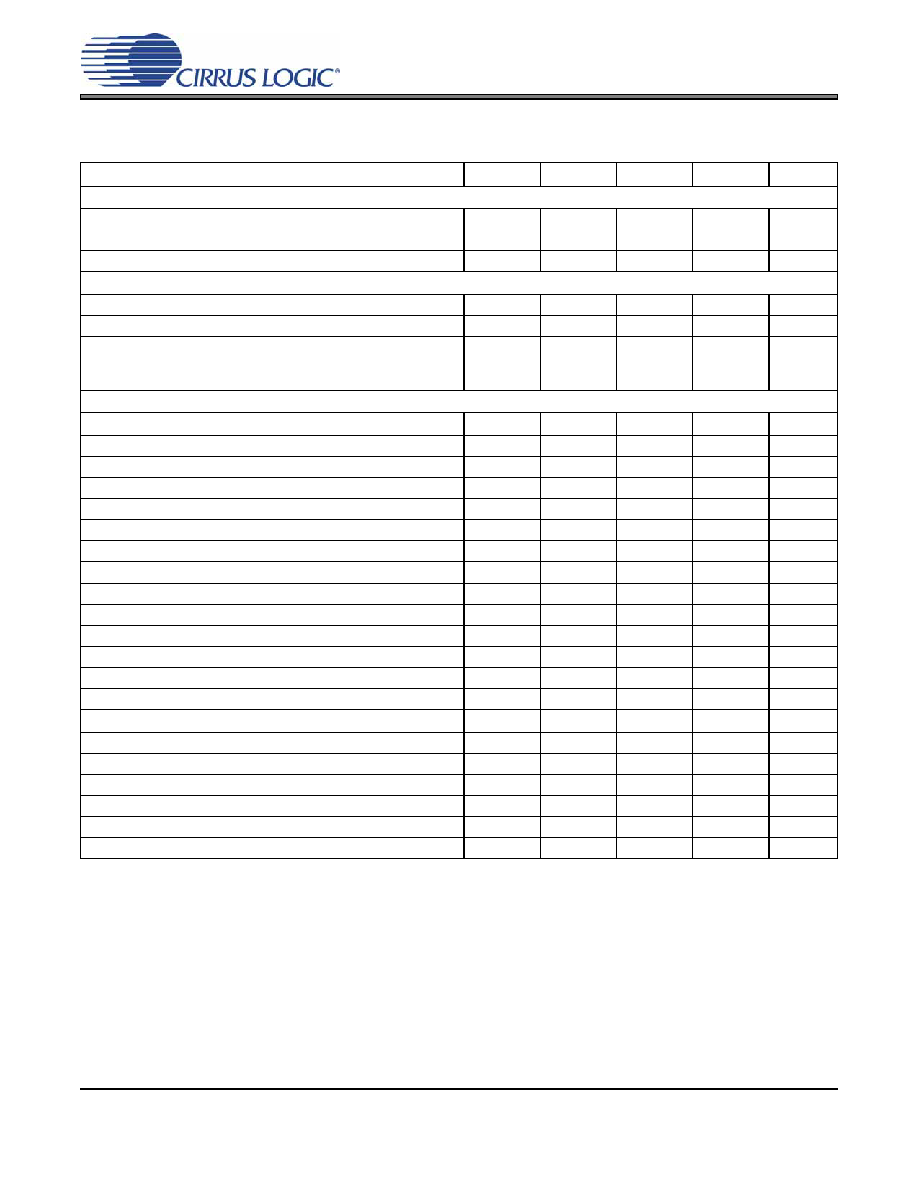

SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT

(Logic "0" = GND = 0 V; Logic "1" = VL, CL = 20 pF)

10. For a description of speed modes, please refer to Table 1 on page 14

11. SCLK must be derived synchronously from MCLK and the ratio of SCLK/LRCK must be equal to 48.

Parameter

Symbol

Min

Typ

Max

Unit

MCLK Specifications

MCLK Period

tclkw

26

-

30

ns

52

-

1302

ns

MCLK Pulse Duty Cycle

40

-

60

%

Master Mode

SCLK falling to LRCK

tmslr

-20

-

20

ns

SCLK falling to SDOUT valid

tsdo

--

32

ns

SCLK Duty Cycle

Single-Speed

Double-Speed

Quad-Speed

-

50

33

-

%

Slave Mode

Single-Speed (Note 10)

LRCK Duty Cycle

40

-

60

%

SCLK Period

tsclkw

313

-

ns

SCLK Duty Cycle

45

-

55

%

SDOUT valid before SCLK rising

tstp

10

-

ns

SDOUT valid after SCLK rising

thld

5-

-

ns

SCLK falling to LRCK edge

tslrd

-20

-

20

ns

Double-Speed (Note 10)

LRCK Duty Cycle

40

-

60

%

SCLK Period (Note 11)

tsclkw

208

-

ns

SCLK Duty Cycle

45

-

55

%

SDOUT valid before SCLK rising

tstp

10

-

ns

SDOUT valid after SCLK rising

thld

5-

-

ns

SCLK falling to LRCK edge

tslrd

-20

-

20

ns

Quad-Speed (Note 10)

LRCK Duty Cycle

40

-

60

%

SCLK Period (Note 11)

tsclkw

104

-

ns

SCLK Duty Cycle

40

-

50

%

SDOUT valid before SCLK rising

tstp

10

-

ns

SDOUT valid after SCLK rising

thld

5-

-

ns

SCLK falling to LRCK edge

tslrd

-8

-

8

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS5345-CQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5345-DQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5346-CQZR

IC ADC AUD 103DB 200KHZ 48-LQFP

CS5351-BZZ

IC ADC AUD 108DB 204KHZ 24-TSSOP

CS5361-DZZ

IC ADC AUD 114DB 204KHZ 24-TSSOP

CS5364-CQZR

IC ADC 4CH 114DB 216KHZ 48-LQFP

CS5366-DQZR

IC ADC 6CH 114DB 216KHZ 48-LQFP

CS5368-DQZ

IC ADC 8CH 114DB 216KHZ 48-LQFP

相关代理商/技术参数

CS5342-CZZR

功能描述:音频模/数转换器 IC IC 105dB 192 kHz Multi-bit Audio ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5342-DZZ

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:105 dB, 192 kHz, MULTI-BIT AUDIO A/D CONVERTER

CS5343

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343_07

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343_08

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:98 dB, 96 kHz, Multi-Bit Audio A/D Converter

CS5343-CZZ

功能描述:音频模/数转换器 IC 98dB 24-Bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5343-CZZR

功能描述:音频模/数转换器 IC IC 98dB 24-bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装:

CS5343-DZZ

功能描述:音频模/数转换器 IC 98dB 24-Bit 96kHz Stereo ADC RoHS:否 制造商:Wolfson Microelectronics 转换速率: 分辨率: ADC 输入端数量: 工作电源电压: 最大工作温度: 最小工作温度: 安装风格: 封装 / 箱体: 封装: